There are two popular types of architectures based on the instruction set. They are CISC (complex instruction set computing) and RISC (Reduced Instruction set computing). Let us discuss the underlying differences, advantages, disadvantages and similarities between these two architectures.

What Is RISC (Reduced Instruction Set Computing)?

RISC (reduced instruction set computer) is a computer that uses a central processing unit (CPU) that implements the processor design principle of simplified instructions. RISC architecture design significantly streamline and accelerate data processing by minimizing the number of instructions permanently stored in the microprocessor and rely more on non-resident instructions i.e code or software programs. RISC is arguably the fastest and most efficient microprocessor technology available today.

RISC chips or microprocessors, take advantage of the fact that most of the instructions for computer processes are relatively simple and computers are design to handle those simple instructions quickly. The RISC architecture is an improvement upon CISC (complex instruction set computing) architecture used in the original Intel Pentium chips. Though Intel has slowly been integrating RISC technology into its chips, but they still are mostly CISC-based.

There is still a lot of controversy among experts about the ultimate value of RISC architectures. The skeptics argue that by making the hardware simpler, RISC architectures put a greater burden on software. They therefore conclude that this is not worth the trouble because conventional microprocessors are increasingly becoming cheap and fast. The proponents on the other hand, argue that RISC machines are both cheaper and faster and are therefore, the machines of the future.

What You Need To Know About RISC Architecture

- RISC has fewer addressing modes and most of the instructions in the instruction set have register to register addressing mode.

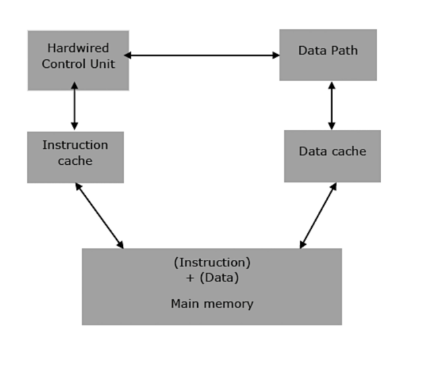

- It is a hard-wired unit of programming.

- Examples of CISC instruction set architectures are system/360, PDP-11, VAX, AMD, Motorola 68000, and desktop PCs on Intel x86 CPUs.

- Fixed-length encodings of the instructions are used. Example: In IA32, generally all instructions are encoded as 4 bytes.

- Arithmetic and logical operations only use register operands. Memory referencing is only allowed by load and store instructions, i.e reading from memory into a register and writing from a register to memory respectively.

- The instruction set is reduced i.e it has only a few instructions in the instruction set. Many of these instructions are very primitive.

- RISC architecture is used in high-end applications such as video processing, telecommunications and image processing.

- RISC processors have simple instructions taking about one clock cycle. The average clock cycle per instruction (CPI) is 1.5.

- RISC processors are highly pipelined.

- Implementation programs are exposed to machine level programs. Few RISC machines do not allow specific instruction sequences.

- Complex addressing modes are synthesized using software.

- The complexity lies in the micro program.

- Performance is optimized with more focus on software.

- It does not require external memory for calculations.

- Decoding of instructions is simple.

- Code expansion can be a problem.

- Execution time is vey less.

- Multiple register sets are present.

- It has no memory unit and uses a separate hardware to implement instructions.

- RISC have a large program size.

What Are Some of The Advantages Of RISC?

- RISC is more of a general approach to computing than a specific set of rules, therefore, different RISC-based processors and systems work in different ways.

- Due its simplicity, it gives the allowance of using the space on microprocessors.

- The speed of the operation can be maximized and the execution time can be minimized.

- It can easily be designed when compared to CISC.

- Performance is better due to simplified instruction set.

- RISC instructions execute one instruction per clock cycle.

- It has a separate unit for memory and therefore disc space can be saved.

Disadvantages Of RISC

- Designing compiler using RISC is complicated.

- It involves more hardware.

- In as much as instruction size are reduced, more number of instructions are required to perform an operation when compared with CISC.

- RISC encounters a lot of difficulty in processing complex instructions and complex addressing mode.

- RISC instructions do not allow direct memory to memory transfer; it requires load and store instructions to do so.

CISC (Complex Instruction Set Computing)

CISC is a type of microprocessor design. The CISC architecture contains a large set of computer instruction that range from very simple to very complex and specialized. Though the design was intended to compute complex instructions in the most efficient way, it was later found that many small, short instructions could compute complex instructions more efficiently.

The PowerPC microprocessor, used in IBM’s RISC system/6000 workstation and Macintosh computers is a RISC microprocessor. Intel’s Pentium microprocessors are CISC microprocessors. RISC takes each of the longer, more complex instructions from a CISC design and reduces it to multiple instructions that are shorter and faster to process.

What You Need To Know About CISC Architecture

- CISC has many different addressing modes and can thus be used to represent higher level programming language statements more efficiently.

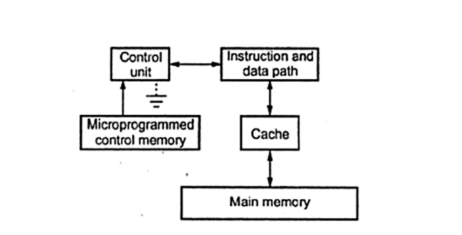

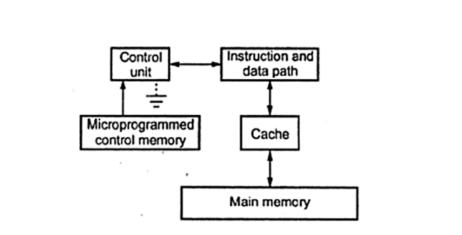

- it has a microprogramming unit.

- Examples of RISC families include DEC Alpha, AMD 29000, ARC, Atmel AVR, Blackfin, Intel i860 and i960, MIPS, Motorola 88000, PA-RISC, power (including PowerPC), SuperH, SPARC and ARM.

- Variable-length encodings of the instructions are used. Example: IA32 instruction size can range from 1 to 15 bytes.

- Arithmetic and logical operations can be applied to both memory and register operands.

- The instruction set has a variety of different instructions that can be used for complex operations.

- CISC architecture is used in low-end applications such as security systems, home automation etc.

- CISC processor has complex instructions that take up multiple clocks for execution. The average clock cycle per instruction (CPI) is in the range of 2 and 15.

- They are normally less pipelined or not pipelined at all.

- Implementation programs are hidden from machine level programs. The ISA provides a clean abstraction between programs and how they get executed.

- CISC already supports complex addressing modes.

- The complexity of RISC lies in the compiler that executes the program.

- Performance is optimized with more focus on hardware.

- It does require an external memory for calculations.

- Decoding of instructions is complex.

- Code expansion is not a problem.

- Execution time is very high.

- Only a single register set is present.

- It has a memory unit to implement complex instructions.

- CISC have a small program size.

What Are Some Of The Advantages Of CISC?

- It is easy to add new commands into the chip without changing the structure of the instruction set as the architecture uses general-purpose hardware to carry out commands.

- It is generally easier to write CISC assembly code than RISC assembly code.

- CISC supports microprogramming.

- Operands in memory are manipulated by instructions.

- CISC have a large number of well defined instructions, a factor that makes high level languages easy to design and implement.

- Has more number of addressing codes and less number of registers.

Disadvantages Of CISC

- They can take multiple cycles per line of code.

- Only less than 30% of the existing instructions are used in a typical programming event, even though there are multiple specialized instructions in existence which are not even used frequently.

- The overall performance of the machine is reduced due to the different amount of clock time required by different instructions.

What Is The Difference Between RISC V And CISC Architecture In Tabular Form

| BASIS OF COMPARISON | RISC | CISC |

| Number Of Addressing Modes | RISC has fewer addressing modes and most of the instructions in the instruction set have register to register addressing mode. | CISC has many different addressing modes and can thus be used to represent higher level programming language statements more efficiently. |

| Microprogramming Unit | It is a hard-wired unit of programming. | It has a microprogramming unit. |

| Examples | System/360, PDP-11, VAX, AMD, Motorola 68000, and desktop PCs on Intel x86 CPUs. | DEC Alpha, AMD 29000, ARC, Atmel AVR, Blackfin, Intel i860 and i960, MIPS, Motorola 88000, PA-RISC, power (including PowerPC), SuperH, SPARC and ARM. |

| Encoding Of Instructions | Fixed-length encodings of the instructions are used. Example: In IA32, generally all instructions are encoded as 4 bytes. | Variable-length encodings of the instructions are used. Example: IA32 instruction size can range from 1 to 15 bytes. |

| Arithmetic And Logical Operations | Arithmetic and logical operations only use register operands. | Arithmetic and logical operations can be applied to both memory and register operands. |

| The Instruction Set | The instruction set is reduced i.e it has only a few instructions in the instruction set. Many of these instructions are very primitive. | The instruction set has a variety of different instructions that can be used for complex operations. |

| Application | It is used in high-end applications such as video processing, telecommunications and image processing. | It is used in low-end applications such as security systems, home automation etc. |

| Processor | Its processors have simple instructions taking about one clock cycle. | Its processor has complex instructions that take up multiple clocks for execution. |

| Processor Pipelining | Its processors are highly pipelined. | Processors are normally less pipelined or not pipelined at all. |

| Implementation programs | Implementation programs are exposed to machine level programs. | Implementation programs are hidden from machine level programs. |

| Complex Addressing Modes | Complex addressing modes are synthesized using software. | It already supports complex addressing modes. |

| Complexity | The complexity lies in the micro program. | The complexity of RISC lies in the compiler that executes the program. |

| Performance | Performance is optimized with more focus on software. | Performance is optimized with more focus on hardware. |

| External Memory | It does not require external memory for calculations. | It does require an external memory for calculations. |

| Decoding Of Instructions | Decoding of instructions is simple. | Decoding of instructions is complex. |

| Code Expansion | Code expansion can be a problem. | Code expansion is not a problem. |

| Execution Time | Execution time is vey less. | Execution time is very high. |

| Registers | Multiple register sets are present. | Only a single register set is present. |

| Memory Unit | It has no memory unit and uses a separate hardware to implement instructions. | It has a memory unit to implement complex instructions. |

| Program Size | RISC have a large program size. | CISC have a small program size. |